**Design Manual**

# **CMOS-N5** Series

# **CMOS Gate Array**

Ver. 7.0

Document No. A13826EJ7V0DM00 (7th edition) Date Published March 2004 N CP(K)

© NEC Electronics Corporation 1998 Printed in Japan [MEMO]

#### **1** VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### **③** PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

**OPENCAD** and **FPBGA** are trademarks of NEC Electronics Corporation.

ModelSim is a registered trademark of Mentor Graphics Corporation.

Design Compiler is a registered trademark of Synopsys, Inc. in Japan.

PrimeTime, TetraMAX, and Formality are registered trademarks of Synopsys, Inc. in the United States.

Verilog, NC-Verilog, Verilog-XL, and Silicon Ensemble are trademarks of Cadence Design Systems, Inc. SUN and Solaris are trademarks of SUN Microsystems, Inc.

Son and Solaris are trademarks of Son microsyste

VCS is a trademark of Synopsys, Inc.

HP and HP-UX are trademarks of Hewlett-Packard Company.

Motif is a trademark of Open Software Foundation, Inc.

Tuxedo and Conformal are trademarks of Verplex Systems, Inc.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of February, 2004. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### [GLOBAL SUPPORT] http://www.necel.com/en/support/support.html

| NEC Electronics America, Inc. (U.S. |

|-------------------------------------|

| Santa Clara, California             |

| Tel: 408-588-6000                   |

| 800-366-9782                        |

.) NEC Electronics (Europe) GmbH NEC Electronics Hong Kong Ltd. Duesseldorf, Germany Tel: 0211-65030

- Sucursal en España Madrid, Spain Tel: 091-504 27 87

- Succursale Francaise Vélizy-Villacoublay, France Tel: 01-30-675800

- Filiale Italiana Milano, Italy Tel: 02-66 75 41

- Branch The Netherlands Eindhoven, The Netherlands Tel: 040-244 58 45

- Tyskland Filial Taeby, Sweden Tel: 08-63 80 820

- United Kingdom Branch Milton Kevnes, UK Tel: 01908-691-133

Hong Kong Tel: 2886-9318

**NEC Electronics Hong Kong Ltd.** Seoul Branch Seoul, Korea Tel: 02-558-3737

**NEC Electronics Shanghai Ltd.** Shanghai, P.R. China Tel: 021-5888-5400

**NEC Electronics Taiwan Ltd.** Taipei, Taiwan Tel: 02-2719-2377

**NEC Electronics Singapore Pte. Ltd.** Novena Square, Singapore Tel: 6253-8311

# Major Revisions in This Edition

| Page                      | Description                                                                                                                            |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Throughout                | <ul> <li>Addition of masters (μPD65891, 65892, 65894)</li> </ul>                                                                       |

|                           | <ul> <li>Transfer of figures and tables in data lists from APPENDIX K DATA to main text and deletion of<br/>APPENDIX K DATA</li> </ul> |

| p.21                      | Modification of Table 1-1 Products                                                                                                     |

| p.26                      | Modification of 2.1.1 Cell utilization rate, usable cell and pin-pair count limits                                                     |

| p.28                      | Modification of Table 2-2 Usable Gates and Pin-Pair Count                                                                              |

| p.46                      | Addition of (3) Mountability based on power supply voltage in 2.1.4 Notes on mounting large-<br>scale macros (memory)                  |

| 6th edition pp.48, 49     | Deletion of 2.2 Package Selection                                                                                                      |

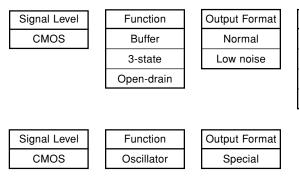

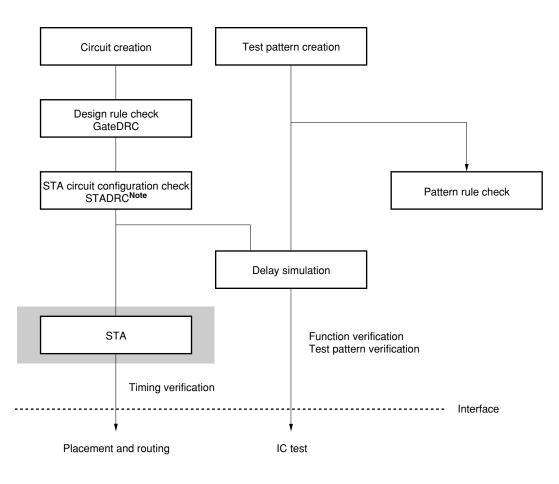

| p.50                      | Modification of Flow 1: Development procedure and interfacing in 2.5 Development Flow                                                  |

| p.53                      | Modification of table in 2.6 OPENCAD Configuration Tools                                                                               |

| pp.55, 56                 | Modification of table in 2.7 List of Interface Data                                                                                    |

| pp.57 to 97               | Modification of 2.8 ASIC Product Development Information                                                                               |

| p.101                     | Modification of Table 3-5 Recommended Operating Range (VDD = 5.0 V ±10%, TA = -40 to +85°C)                                            |

| p.107                     | Modification of Table 3-11 Recommended Operating Range (VDD = 3.3 ±0.3 V, TA = -40 to +85°C)                                           |

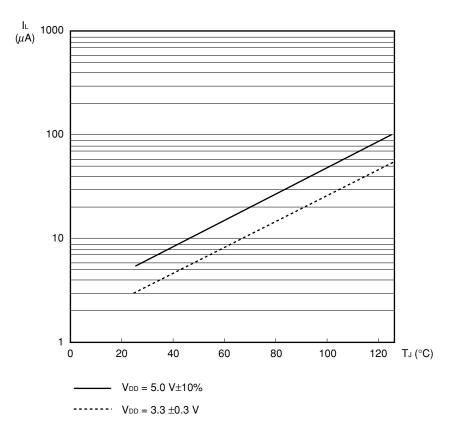

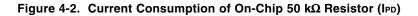

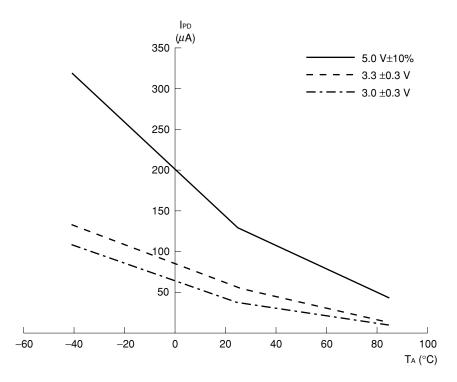

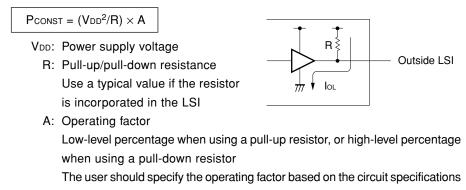

| pp.112, 114               | Modification of 4.1.1 Estimating static current consumption                                                                            |

| p.121                     | Modification of Figure 4-12 Oscillator Configuration Diagram                                                                           |

| p.126                     | Modification of 4.3.4 Compensation method                                                                                              |

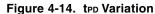

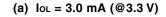

| pp.132 to 135             | Modification of 4.4.4 Fluctuation in propagation delay time                                                                            |

| p.138                     | Modification of Table 4-9 Recommended Load Capacitance Ranges of Output Buffers (@3.3 V)                                               |

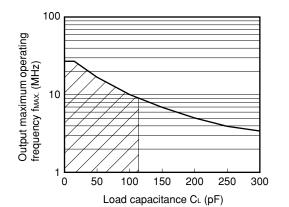

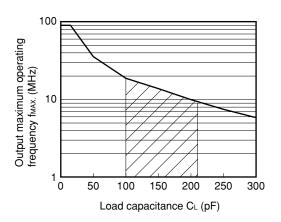

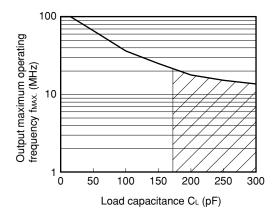

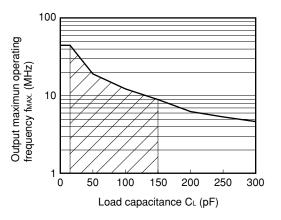

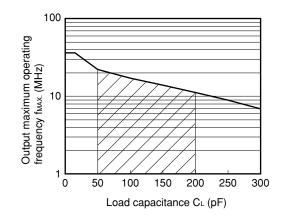

| p.139                     | Modification of (a) IoL = 3.0 mA (@3.3 V) in Figure 4-15 fMAX. vs. CL Limit (CMOS Level Output)                                        |

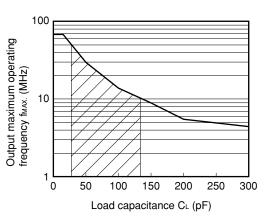

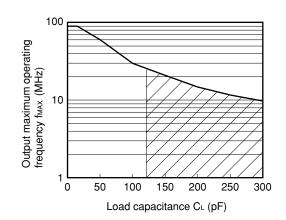

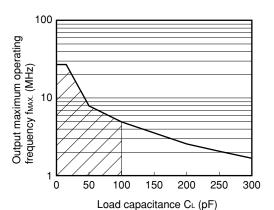

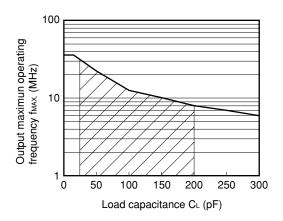

| p.141                     | Modification of (a) IoL = 3.0 mA (@3.3 V) in Figure 4-16 fmax. vs. CL Limit (CMOS Level Low-Noise                                      |

|                           | Output)                                                                                                                                |

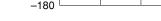

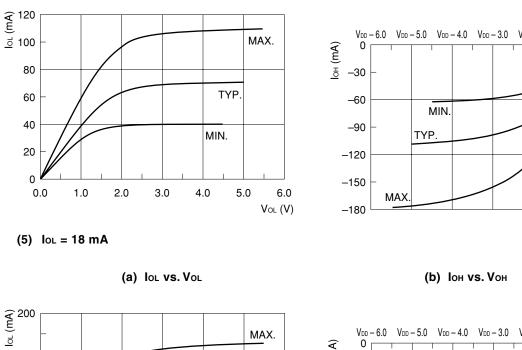

| pp.147, 148               | Modification of description in Figure 4-20 Io vs. Vo (@3.3 V)                                                                          |

| p.153                     | Modification of description in 4.6.4 Simultaneous operation pins to be checked                                                         |

| p.154                     | Modification of calculation example in 4.6.6 Three-GND-pin determination                                                               |

| pp.173, 174               | Addition of Caution in 5.4.3 Clock tree synthesis                                                                                      |

| p.206                     | Modification of description in 6.2.3 Number of test patterns                                                                           |

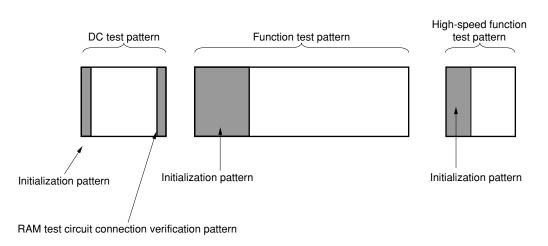

| p.215                     | Modification of description in 6.5 Test Pattern for On-Chip RAM                                                                        |

| p.229                     | Addition of 7.3.3 Using oscillator (resonator) and CTS together                                                                        |

| pp.230, 231               | Addition of descriptions in 7.3.4 Notes on configuring an oscillator                                                                   |

| p.231                     | Addition of Figure 7-6 Example of Overtone Circuits                                                                                    |

| pp.233, 234               | Modification of Table 7-3 List of Resonator Evaluations                                                                                |

| p.244                     | Modification of 7.6.3 Checking connection of RAM test circuit                                                                          |

| p.252                     | Modification of description in C.2 (4) Example                                                                                         |

| pp.261 to 287             | Modification of APPENDIX E LIST OF BLOCKS                                                                                              |

| 6th edition pp.261 to 270 | Deletion of APPENDIX F PIN DESCRIPTIONS                                                                                                |

| 6th edition pp.271 to 274 | Deletion of APPENDIX G PINS ASSIGNABLE TO OSCILLATOR                                                                                   |

| 6th edition pp.275 to 285 | Deletion of APPENDIX H PACKAGE DRAWINGS                                                                                                |

| 6th edition pp.286 to 288 | Deletion of APPENDIX I PACKAGE MARKINGS                                                                                                |

| 6th edition pp.289 to 290 | Deletion of APPENDIX J RECOMMENDED SOLDERING CONDITIONS                                                                                |

The mark  $\star$  shows major revised points.

#### INTRODUCTION

This manual explains the restrictions and points to be noted when designing LSIs using NEC Electronics' CMOS-N5 Series of high-speed, high-density CMOS gate arrays.

In order to ensure smooth design of an LSI, read this manual carefully.

Be sure to follow the specifications described in this manual (including general information, cautions, and restrictions). Failure to do so may result in poor quality, poor performance, or operational faults in LSI products.

The following abbreviations are used for the package names in this manual.

| Abbreviation | Standard Package Name  |

|--------------|------------------------|

| QFP          | Plastic QFP            |

| PBGA         | Plastic BGA            |

| TBGA         | Tape BGA               |

| FPBGA™       | Fine pitch plastic BGA |

#### **Regarding the Order of Masters**

Each of the information is described in gate size order, not in master order.

| Target Readers          | This manual is intended for user engineers who wish to design an LSI using the CMOS-N5 Series.                                                  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose                 | This manual explains general information, limitations, and points to be noted when designing an LSI using the CMOS-N5 Series.                   |

| How to Read This Manual | It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcomputers. |

|                         | • To understand the overall functions of the CMOS-N5 Series: $\rightarrow$ Read this manual in the order of the contents.                       |

See CMOS Gate Array, Embedded Array Package Design Manual (A16400E) for the following items.

- · List of packages

- Maximum allowable power consumption

- Thermal resistance

- · Assignment of VDD, GND, NC, SCAN test pins

- · Pins that can be used for oscillators

- Package drawings

- Package markings

- · Mounting rank (Recommended soldering conditions)

| Conventions | Note:    | Footnote for item marked with $\ensuremath{\textbf{Note}}$ in the text |

|-------------|----------|------------------------------------------------------------------------|

|             | Caution: | Information requiring particular attention                             |

|             | Remark:  | Supplementary information                                              |

#### **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

| • | CMOS-N5 Series Design Manual                                           | (This manual) |

|---|------------------------------------------------------------------------|---------------|

| • | CMOS-N5 Series (5.0 V) Block Library                                   | (A13872E)     |

| • | CMOS-N5 Series (3.3 V) Block Library                                   | (A15895E)     |

| • | CMOS-N5 Series Memory Block Library                                    | (A14683E)     |

| • | CMOS-N5 Series Mega Macro Design Manual                                | (A14759E)     |

| • | CMOS Gate Array, Embedded Array Package Design Manual                  | (A16400E)     |

| • | NEC SYSTEM LSI DESIGN OPENCAD <sup>™</sup> OPC_VSHELL User's Manual    | (A16306E)     |

| • | NEC SYSTEM LSI DESIGN Design For Test TESTACT, NEC_SCAN2 User's Manual | (A16437E)     |

| • | NEC SYSTEM LSI DESIGN Design For Test NEC_BIST, NEC_TESTBUS,           |               |

|   | NEC_SCAN/SCAN2, NEC_BSCAN/BSCAN2 User's Manual                         | (A15168E)     |

| • | SEMICONDUCTOR SELECTION GUIDE -Products and Packages-                  | (X13769X)     |

To obtain the latest documents when designing, contact an NEC Electronics sales office or distributor.

### CONTENTS

| CHAP | TER 1                     | OVERVIEW                                                               | 19 |

|------|---------------------------|------------------------------------------------------------------------|----|

| 1.1  | Foatu                     | res                                                                    | 10 |

| 1.2  |                           |                                                                        |    |

| 1.3  |                           | al Structure of CMOS-N5 Series                                         |    |

| 1.4  | 4 Internal Cell Structure |                                                                        |    |

| 1.5  |                           |                                                                        |    |

|      |                           |                                                                        |    |

| CHAP | TER 2                     | IMPLEMENTING THE SYSTEM USING THE GATE ARRAY                           | 25 |

| 2.1  | Estim                     | ating Circuit Scale                                                    | 26 |

|      | 2.1.1                     | Cell utilization rate, usable cell and pin-pair count limits           | 26 |

|      | 2.1.2                     | Notes on estimating number of cells used                               | 29 |

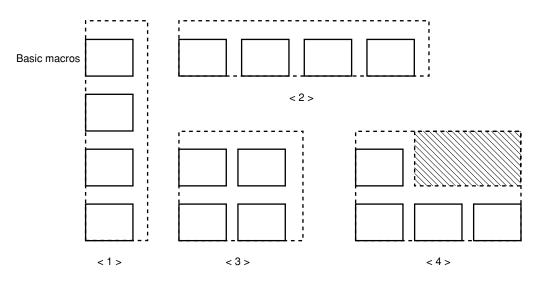

|      | 2.1.3                     | Large-scale macro mounting                                             | 29 |

|      | 2.1.4                     | Notes on mounting large-scale macros (memory)                          | 46 |

| 2.2  | Verify                    | ing Power Consumption                                                  | 46 |

| 2.3  | Pin Pl                    | acement                                                                | 47 |

|      | 2.3.1                     | Notes on pin layout                                                    | 47 |

| 2.4  | I/O Int                   | erface                                                                 | 48 |

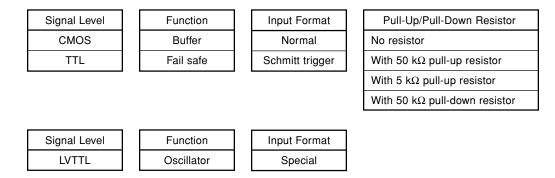

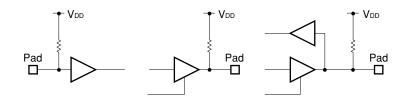

|      | 2.4.1                     | Input blocks                                                           | 48 |

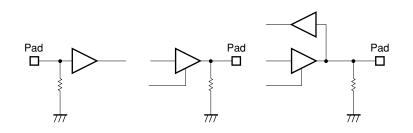

|      | 2.4.2                     | Output blocks                                                          | 49 |

| 2.5  |                           | opment Flow                                                            |    |

| 2.6  |                           | CAD Configuration Tools                                                |    |

| 2.7  |                           | f Interface Data                                                       |    |

| 2.8  | ASIC                      | Product Development Information                                        |    |

|      | 2.8.1                     | ASIC product development information (checksheet)                      |    |

|      | 2.8.2                     | RAM block                                                              | 74 |

|      | 2.8.3                     | ROM                                                                    |    |

|      | 2.8.4                     | High-speed function test                                               | 80 |

|      | 2.8.5                     | GTL, PECL, HSTL, PCI, LVDS block                                       |    |

|      | 2.8.6                     | DPLL block                                                             |    |

|      | 2.8.7                     | Megamacro                                                              |    |

|      | 2.8.8                     | Alternate use as scan path and boundary scan                           | 90 |

|      | 2.8.9                     | Scan path                                                              |    |

|      | 2.8.10                    | Boundary scan                                                          |    |

| CHAP | TER 3                     | PRODUCT SPECIFICATIONS                                                 | 98 |

| 3.1  | Termi                     | nology                                                                 |    |

| 3.2  |                           | ute Maximum Ratings                                                    |    |

| 3.3  |                           | ard Specification of CMOS Interface Conditions (VDD = 5.0 V $\pm$ 10%, |    |

|      |                           | 40 to +85°C)                                                           |    |

|      | 3.3.1                     | Recommended operating range                                            |    |

|      | 3.3.2                     | DC characteristics                                                     |    |

|      | 3.3.3                     | AC characteristics                                                     |    |

|      | -                         |                                                                        |    |

| 3.4  | Speci | fication 1 (Vdd = 3.0 $\pm$ 0.3 V, TA = –40 to +85°C)   | 104 |

|------|-------|---------------------------------------------------------|-----|

|      | 3.4.1 | Recommended operating range                             | 104 |

|      | 3.4.2 | DC characteristics                                      | 105 |

|      | 3.4.3 | AC characteristics                                      | 106 |

| 3.5  | Speci | fication 2 (Vdd = 3.3 $\pm$ 0.3 V, TA = –40 to +85°C)   | 107 |

|      | 3.5.1 | Recommended operating range                             |     |

|      | 3.5.2 | DC characteristics                                      |     |

|      | 3.5.3 | AC characteristics                                      |     |

| 3.6  | Pin C | apacitance                                              | 109 |

| СНАР | TER 4 | ESTIMATING ELECTRICAL CHARACTERISTICS                   | 111 |

| 4.1  | Estim | ating Static Current Consumption                        | 111 |

|      | 4.1.1 | Estimating static current consumption                   |     |

| 4.2  | Input | Through Current                                         |     |

| 4.3  | •     | r Consumption                                           |     |

|      | 4.3.1 | Causes of power consumption                             |     |

|      | 4.3.2 | Estimating power consumption                            |     |

|      | 4.3.3 | Unit power consumption of memory                        |     |

|      | 4.3.4 | Compensation method                                     |     |

|      | 4.3.5 | Determining power consumption                           |     |

| 4.4  |       | gation Delay Time                                       |     |

|      | 4.4.1 | Accuracy of propagation delay time                      |     |

|      | 4.4.2 | Calculation in propagation delay time                   |     |

|      | 4.4.3 | Estimating wiring capacitance                           |     |

|      | 4.4.4 | Fluctuation in propagation delay time                   |     |

| 4.5  | Outpu | It Buffer Characteristics                               |     |

|      | 4.5.1 | Output buffer rise and fall times                       |     |

|      | 4.5.2 | Recommended load capacitance range of output buffers    |     |

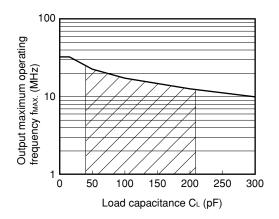

|      | 4.5.3 | Maximum operating frequency of output buffers           |     |

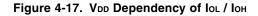

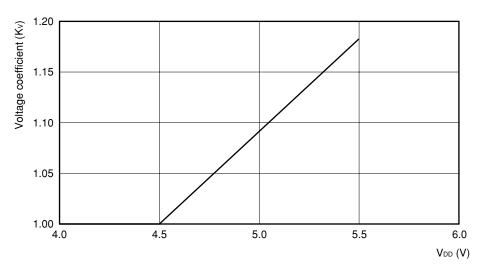

|      | 4.5.4 | Output buffer output current (Io⊢, Ioн)                 |     |

| 46   |       | ictions to Simultaneous Operation of Output Buffers     |     |

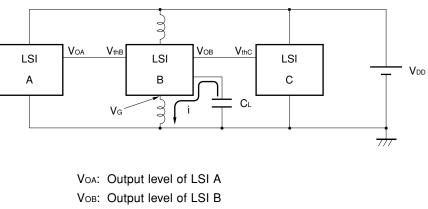

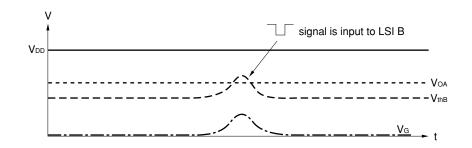

| 4.0  | 4.6.1 | Malfunction due to simultaneous operation of outputs    |     |

|      | 4.6.2 | Definitions                                             |     |

|      | 4.6.3 | Factors for the determination of simultaneous operation |     |

|      | 4.6.4 | Simultaneous operation pins to be checked               |     |

|      | 4.6.5 | Pin placement and simultaneous operation                |     |

|      | 4.6.6 | Three-GND-pin determination                             |     |

|      | 4.6.7 | Assumptions for the determination method                |     |

|      | 4.6.8 | Other determination methods                             |     |

|      | 4.0.0 |                                                         |     |

| CHAP | TER 5 | CIRCUIT DESIGN GUIDELINES                               | 159 |

| 5.1  |       | Circuit Configuration                                   |     |

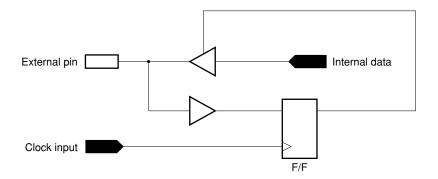

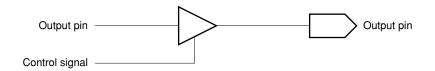

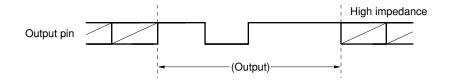

|      | 5.1.1 | Using I/O buffers                                       |     |

|      | 5.1.2 | Unused pins                                             |     |

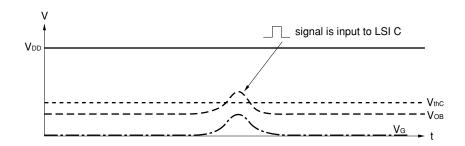

|      | 5.1.3 | Fan-out limitations                                     |     |

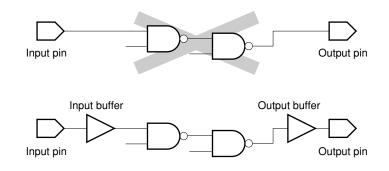

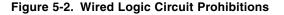

|      | 5.1.4 | Wired logic circuit prohibitions                        | 160 |

|      | 5.1.5   | Notes on using bidirectional buffers                  | 161 |

|------|---------|-------------------------------------------------------|-----|

| 5.2  | Differ  | ential Circuit Prohibition                            |     |

| 5.3  | RS La   | tch and Loop Circuits                                 |     |

|      | 5.3.1   | RS latch                                              |     |

|      | 5.3.2   | Loop circuit                                          |     |

|      | 5.3.3   | Prohibited state of flip-flops                        |     |

| 5.4  | Clock   | ed Signal Design                                      | 166 |

|      | 5.4.1   | Synchronous circuit design                            |     |

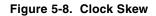

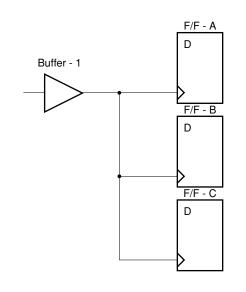

|      | 5.4.2   | Clock skew                                            | 171 |

|      | 5.4.3   | Clock tree synthesis                                  |     |

| 5.5  | Notes   | on Configuring High-Speed Circuits                    | 178 |

| 5.6  | Delay   | Time Margin                                           | 179 |

|      | 5.6.1   | Timing definitions                                    |     |

|      | 5.6.2   | Delay time margin calculation (asynchronous circuits) |     |

|      | 5.6.3   | Delay time margin calculation (high-speed circuits)   |     |

|      | 5.6.4   | Minimum pulse width                                   |     |

|      | 5.6.5   | Metastable state (preliminary)                        |     |

|      | 5.6.6   | Critical paths                                        |     |

|      | 5.6.7   | Ensuring operating margin                             | 193 |

| 5.7  | Intern  | al Bus Configuration                                  | 194 |

|      | 5.7.1   | Configuring internal bus                              |     |

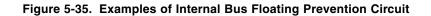

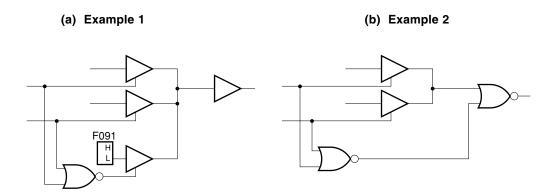

|      | 5.7.2   | Preventing internal bus floating                      | 194 |

|      | 5.7.3   | Precautions when using internal bus                   | 195 |

| 5.8  | Preve   | nting Contention with External Bus                    |     |

| 5.9  | Testal  | bility                                                | 197 |

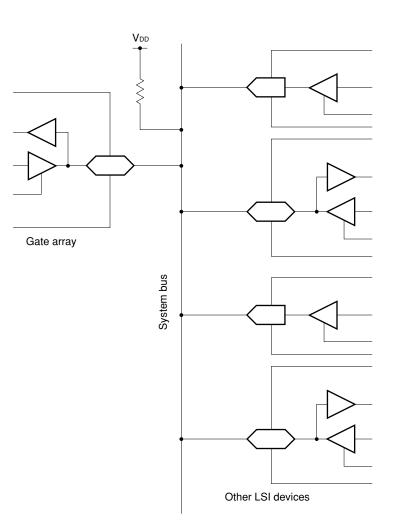

|      | 5.9.1   | Flip-flop initial setting                             | 197 |

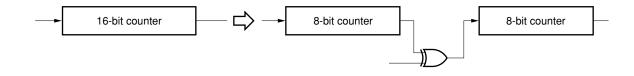

|      | 5.9.2   | Counter division                                      | 197 |

|      | 5.9.3   | Adding test pins and dividing circuits                | 198 |

| 5.10 | ) Racin | g and Spike Noise                                     |     |

|      | 5.10.1  | Racing (contention)                                   | 199 |

|      | 5.10.2  | Spike noise                                           |     |

| СНАР | TER 6   | TEST PATTERN GENERATION                               | 204 |

|      | _       |                                                       |     |

| 6.1  |         | Pattern Types                                         |     |

| 6.2  |         | from Viewpoint of Product Test (LSI Tester)           |     |

|      | 6.2.1   | I/O pin naming conventions                            |     |

|      | 6.2.2   | Limitations on test pattern length                    |     |

|      | 6.2.3   | Number of test patterns                               |     |

| 6.3  |         | on Creating Test Pattern for Function Test            |     |

|      | 6.3.1   | Initializing circuit                                  |     |

|      | 6.3.2   | Test cycle (test rate)                                |     |

|      | 6.3.3   | Output determination time (strobe time)               |     |

|      | 6.3.4   | Specification of timing phase                         |     |

|      | 6.3.5   | Skew                                                  |     |

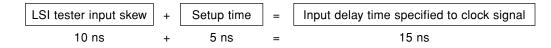

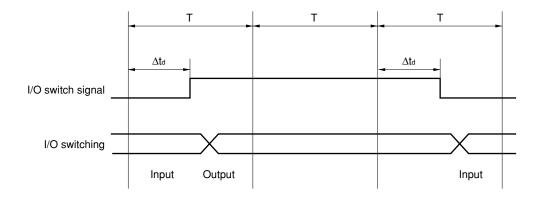

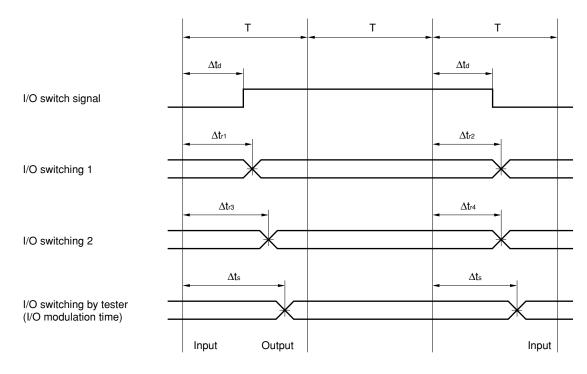

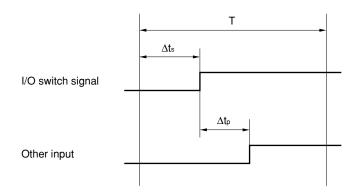

|      | 6.3.6   | Notes on switching I/O mode of bidirectional pin      |     |

|      | 6.3.7   | I/O modulation function                               |     |

|      | 6.3.8   | I/O conflict                                          |     |

|      | 6.3.9  | Testing multifunction I/O circuits                                    | 213 |

|------|--------|-----------------------------------------------------------------------|-----|

| 6.4  | Notes  | on Creating DC Test Patterns                                          | 214 |

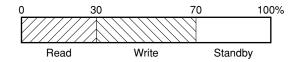

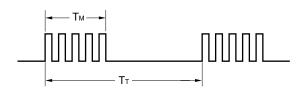

| 6.5  | Test F | Pattern for On-Chip RAM                                               | 215 |

| 6.6  |        | Speed Function Test (Real-Time Test)                                  |     |

|      | 6.6.1  | Limitation of the test pattern length                                 |     |

|      | 6.6.2  | Test cycle (test rate)                                                | 216 |

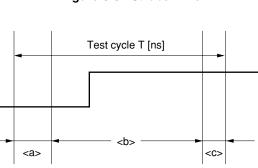

|      | 6.6.3  | Output determination time (strobe time)                               | 216 |

|      | 6.6.4  | Notes on high-speed function testing                                  | 217 |

| 6.7  | Testal | pility (Fault Coverage)                                               |     |

|      | 6.7.1  | Consideration of testability (fault coverage)                         | 219 |

|      | 6.7.2  | Principle of fault simulation                                         | 219 |

| 6.8  | Consi  | deration of System Simulation                                         | 222 |

| СНАР | TER 7  | MULTIFUNCTION BLOCKS                                                  | 223 |

| 7.1  | Buffe  | r with Fail-Safe Function                                             | 224 |

| 7.2  |        | Output/Bidirectional Buffers with On-Chip Pull-Up/Pull-Down Resistors |     |

| 7.3  |        | ator                                                                  |     |

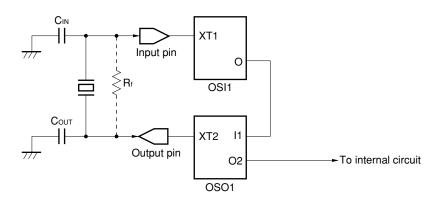

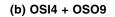

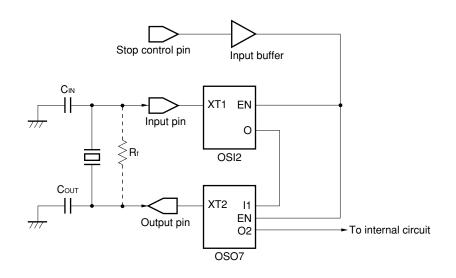

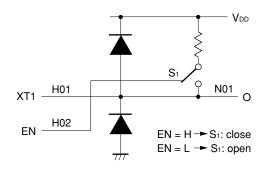

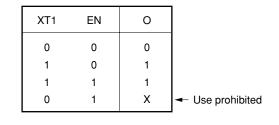

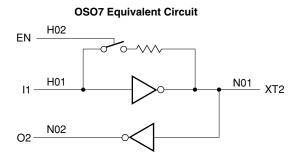

|      | 7.3.1  | Configuration of oscillator                                           | 226 |

|      | 7.3.2  | Description of oscillator                                             |     |

| *    | 7.3.3  | Using oscillator (resonator) and CTS together                         | 229 |

|      | 7.3.4  | Notes on configuring an oscillator                                    |     |

|      | 7.3.5  | Constants of external circuit                                         |     |

| 7.4  | Memo   | ry                                                                    |     |

|      | 7.4.1  | Types of memory blocks                                                |     |

|      | 7.4.2  | RAM blocks                                                            |     |

| 7.5  | Writin | g Memory Blocks                                                       | 238 |

|      | 7.5.1  | Selecting memory blocks                                               |     |

|      | 7.5.2  | Using memory blocks                                                   |     |

| 7.6  | Memo   | ry Test                                                               | 239 |

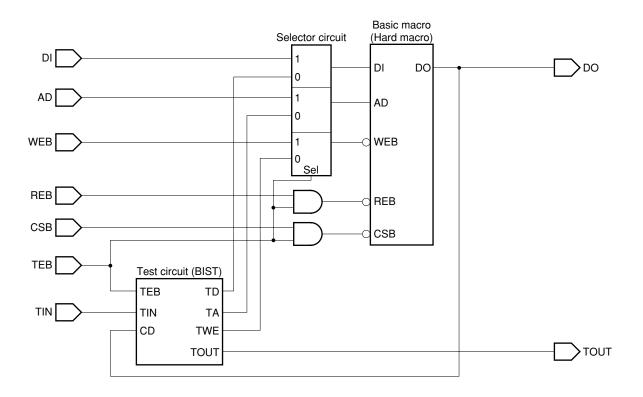

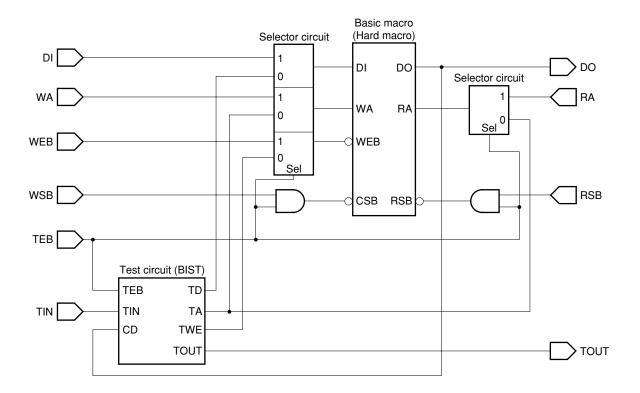

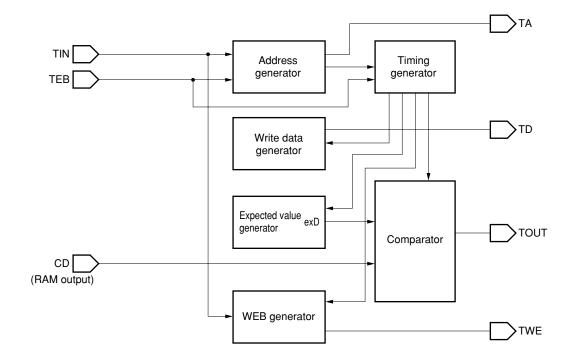

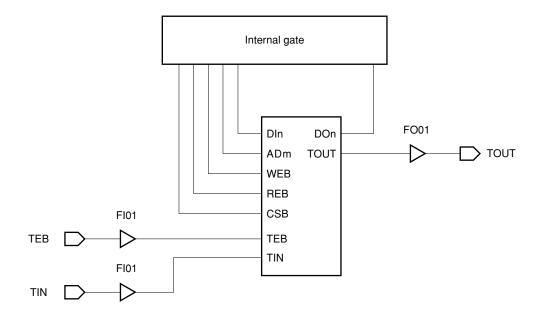

|      | 7.6.1  | RAM test                                                              | 239 |

|      | 7.6.2  | Assigning test I/O pins (TIN, TEB, and TOUT)                          | 242 |

|      | 7.6.3  | Checking connection of RAM test circuit                               |     |

| 7.7  | Scan   | Path Test Block                                                       |     |

|      |        | POWER CONSUMPTION (PRELIMINARY)                                       |     |

|      |        | ALBATROSS AND DIF FILE FORMATS                                        |     |

|      |        | TROSS File Format (Circuit Name.alb)                                  |     |

| C.2  | DIF Fi | le Format (Circuit Name.dif)                                          | 251 |

| APPE | NDIX D | DRAWING CIRCUIT DIAGRAMS AND TIMING CHARTS                            | 253 |

| D.1  | Drawi  | ng Circuit Diagrams                                                   | 253 |

|      | D.1.1  | Logic symbols                                                         |     |

|      |        |                                                                       |     |

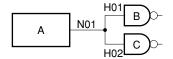

|       | D.1.2   | Block names (function names)                           | 253 |

|-------|---------|--------------------------------------------------------|-----|

|       | D.1.3   | Pin names (I/O pin name of block)                      | 253 |

|       | D.1.4   | Gate names (specific name of each block)               | 253 |

|       | D.1.5   | I/O pin names                                          |     |

| D.2   | Handli  | ng Macros                                              | 257 |

| D.3   | Prepa   | ring Timing Charts                                     | 259 |

| APPEI | NDIX E  | LIST OF BLOCKS                                         | 261 |

| E.1   | Interfa | ce Block                                               | 261 |

|       | E.1.1   | CMOS Level                                             |     |

|       | E.1.2   | TTL Level                                              |     |

|       | E.1.3   | Oscillator                                             | 273 |

| E.2   | Functi  | on Block                                               | 274 |

|       | E.2.1   | Level Generator                                        | 274 |

|       | E.2.2   | Inverter, Buffer, CTS Driver, Delay Gate               | 274 |

|       | E.2.3   | OR(NOR)                                                | 275 |

|       | E.2.4   | AND(NAND)                                              | 276 |

|       | E.2.5   | AND-NOR                                                | 277 |

|       | E.2.6   | OR-NAND                                                | 278 |

|       | E.2.7   | Exclusive OR, Exclusive NOR                            | 279 |

|       | E.2.8   | Adder, 3-State Buffer, Decoder, Multiplexer, Generator |     |

|       | E.2.9   | RS-Latch, RS-F/F                                       |     |

|       | E.2.10  | D-Latch                                                | 281 |

|       | E.2.11  | D-F/F                                                  | 282 |

|       | E.2.12  | T-F/F, JK-F/F                                          | 284 |

| E.3   | Scan I  | Path Block                                             | 285 |

|       | E.3.1   | Standard Type                                          | 285 |

|       | E.3.2   | NEC Scan                                               | 285 |

|       | E.3.3   | Scan Controller                                        | 286 |

| E.4   | Bound   | lary Scan Block                                        |     |

|       | E.4.1   | TAP Macro                                              | 287 |

|       | E.4.2   | Level Generator                                        |     |

|       | E.4.3   | Data Register                                          |     |

|       | E.4.4   | D-latch, Selector, Shift Register                      |     |

|       | E.4.5   | Soft Macro                                             | 287 |

# LIST OF FIGURES (1/3)

| Figure No. Title |                                                              | Pag |  |

|------------------|--------------------------------------------------------------|-----|--|

| 1-1              | Gate Array Configuration                                     |     |  |

| 1-2              | Internal Cell Equivalent Circuit                             |     |  |

| 1-3              | Equivalent Circuits                                          |     |  |

| 1-4              | Cross-Section of QFP Package                                 | 24  |  |

| 2-1              | Pin-Pair Count                                               |     |  |

| 2-2              | Shape of Cell Range Occupied by Macros (with 4 Basic Macros) |     |  |

| 2-3              | Cell Range Occupied by Macro                                 |     |  |

| 2-4              | Area Where Macros Cannot Be Implemented                      |     |  |

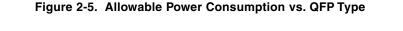

| 2-5              | Allowable Power Consumption vs. QFP Type                     |     |  |

| 4-1              | Leakage Current                                              | 112 |  |

| 4-2              | Current Consumption of On-Chip 50 k $\Omega$ Resistor (IPD)  | 113 |  |

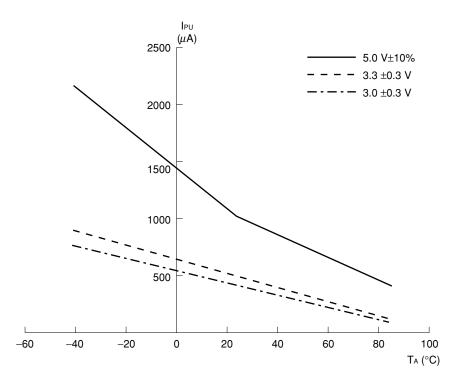

| 4-3              | Current Consumption of On-Chip 5 k $\Omega$ Resistor (IPU)   | 113 |  |

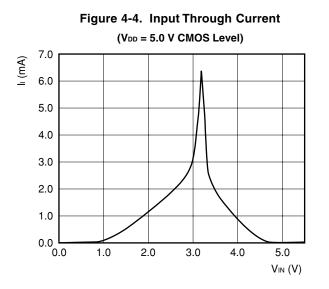

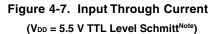

| 4-4              | Input Through Current (VDD = 5.0 V CMOS Level)               | 115 |  |

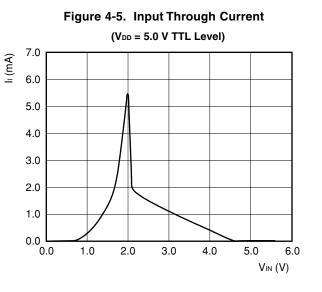

| 4-5              | Input Through Current (VDD = 5.0 V TTL Level)                | 115 |  |

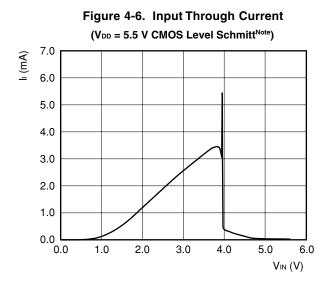

| 4-6              | Input Through Current (VDD = 5.5 V CMOS Level Schmitt)       | 115 |  |

| 4-7              | Input Through Current (VDD = 5.5 V TTL Level Schmitt)        | 115 |  |

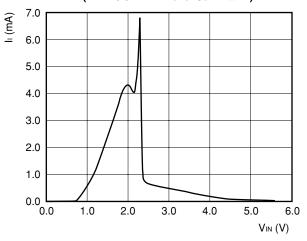

| 4-8              | Input Through Current (VDD = 3.6 V CMOS Level)               | 116 |  |

| 4-9              | Input Through Current (VDD = 3.3 V TTL Level)                | 116 |  |

| 4-10             | Input Through Current (VDD = 3.6 V CMOS Level Schmitt)       | 116 |  |

| 4-11             | Input Through Current (VDD = 3.3 V TTL Level Schmitt)        | 116 |  |

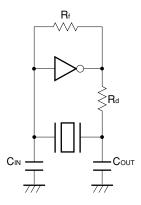

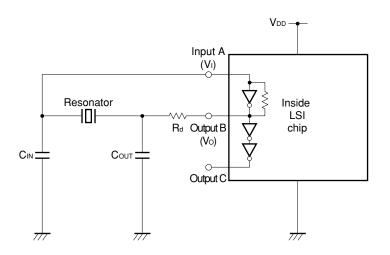

| 4-12             | Oscillator Configuration Diagram                             | 121 |  |

| 4-13             | Propagation Delay Time                                       | 134 |  |

| 4-14             | tpd Variation                                                | 135 |  |

| 4-15             | fMAX. vs. CL Limit (CMOS Level Output)                       | 139 |  |

| 4-16             | fMAX. vs. CL Limit (CMOS Level Low-Noise Output)             | 141 |  |

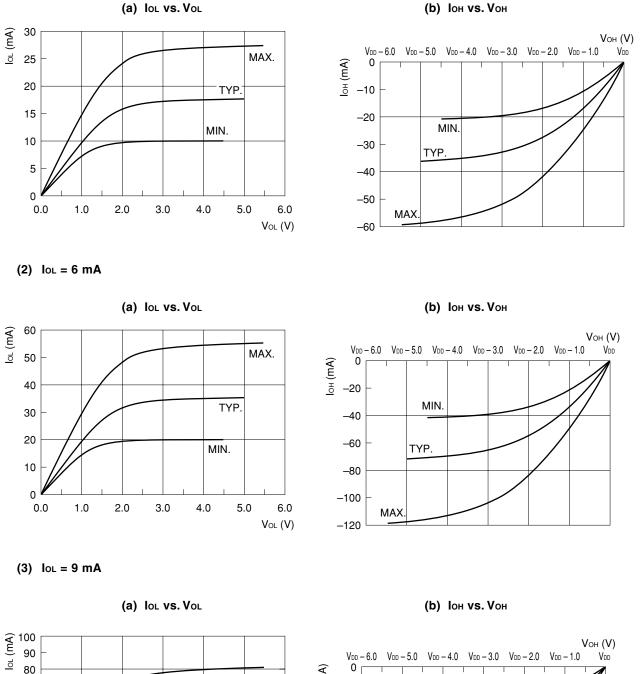

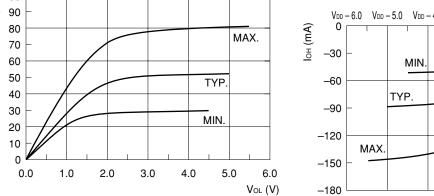

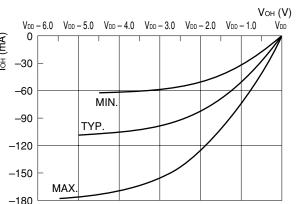

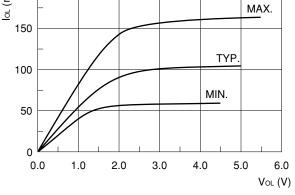

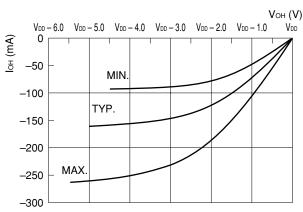

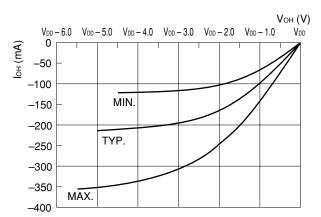

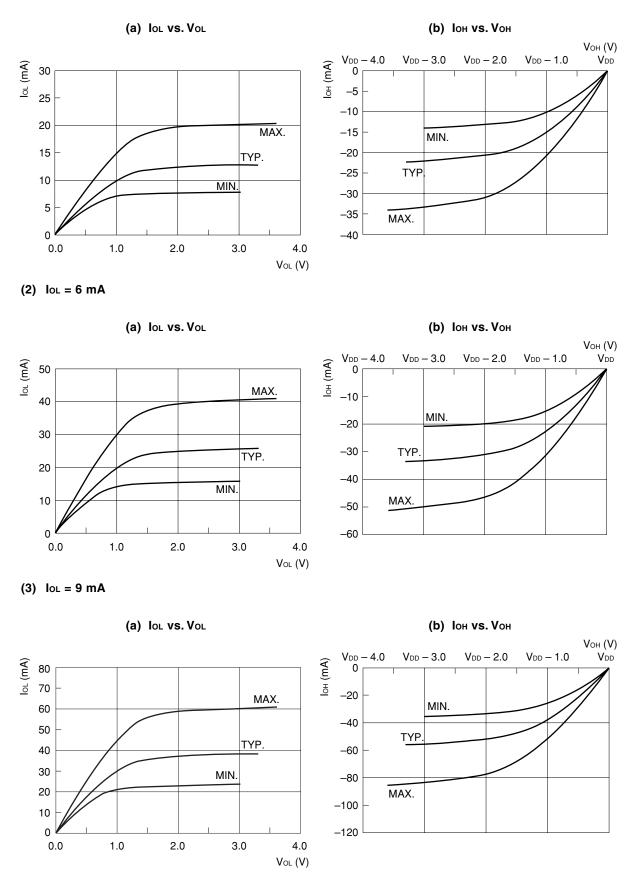

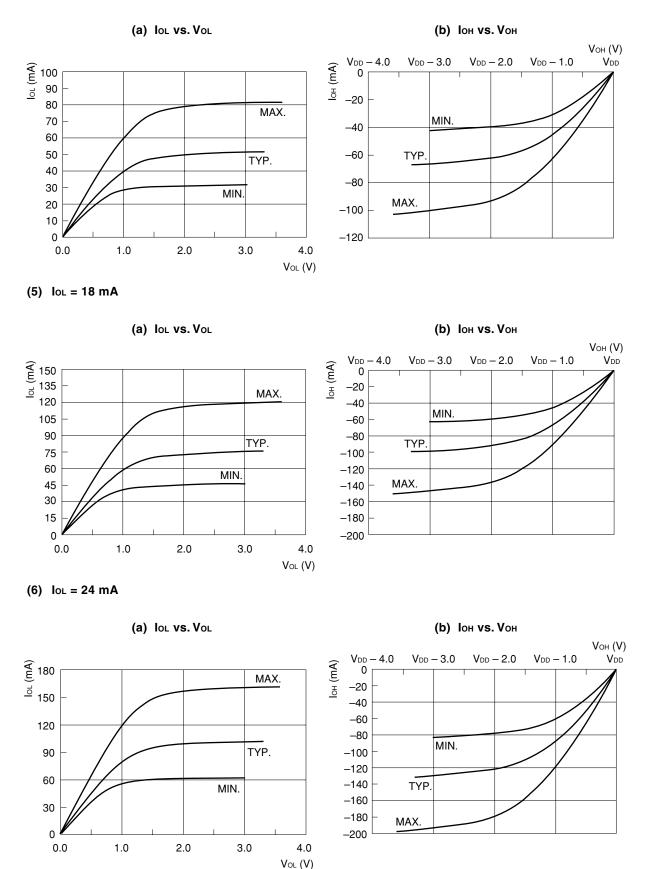

| 4-17             | Vdd Dependency of IoL / Ioн                                  | 143 |  |

| 4-18             | Та Dependency of IoL / Ioн                                   | 144 |  |

| 4-19             | lo vs. Vo (@5.0 V)                                           | 145 |  |

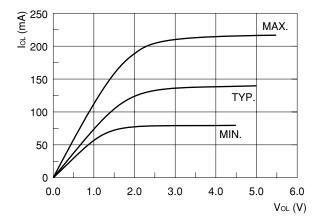

| 4-20             | lo vs. Vo (@3.3 V)                                           | 147 |  |

| 4-21             | Malfunction Caused by Simultaneous Operation                 | 150 |  |

| 5-1              | Basic Circuit Configuration                                  | 159 |  |

| 5-2              | Wired Logic Circuit Prohibitions                             |     |  |

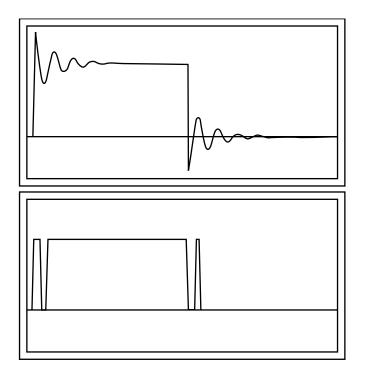

| 5-3              | Ringing                                                      |     |  |

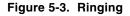

| 5-4              | Example of Preventive Circuit                                | 161 |  |

| 5-5              | Differential Circuit Prohibition                             | 162 |  |

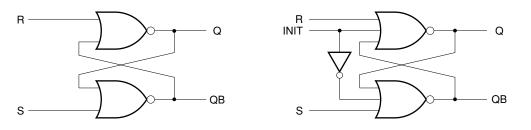

| 5-6              | Asynchronous RS Latches                                      | 163 |  |

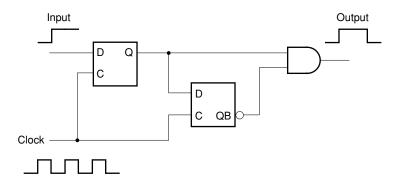

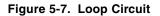

| 5-7              | Loop Circuit                                                 | 164 |  |

| 5-8              | Clock Skew                                                   | 167 |  |

| 5-9              | Clock Skew Countermeasure 1                                  | 168 |  |

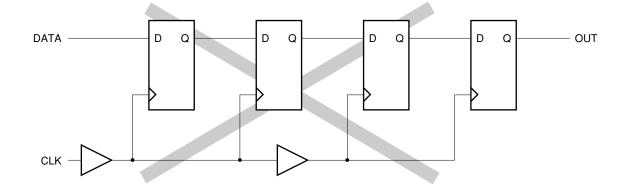

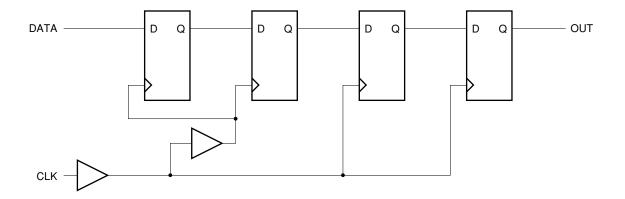

| 5-10             | Clock Skew Countermeasure 2                                  | 169 |  |

# LIST OF FIGURES (2/3)

| Figur | re No. Title                                                  | Page |

|-------|---------------------------------------------------------------|------|

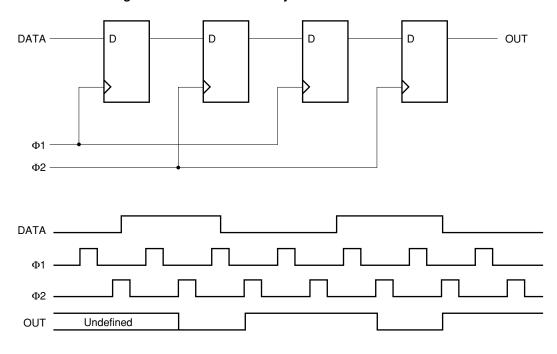

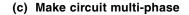

| 5-11  | Double-Phase Synchronous Circuit                              | 170  |

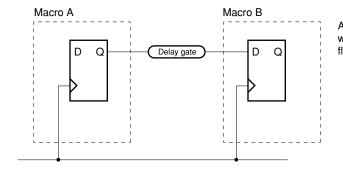

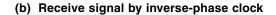

| 5-12  | Countermeasures for Clock Lines Between Macros                |      |

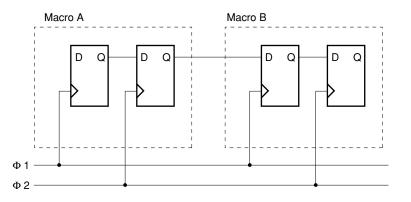

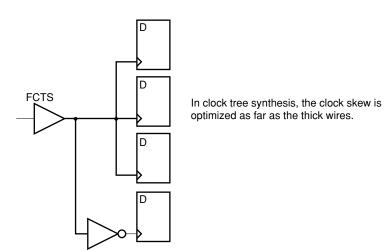

| 5-13  | Concept of CTS                                                |      |

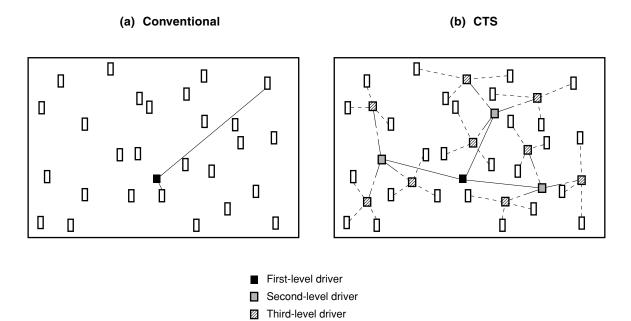

| 5-14  | Image of CTS Use (Example of FC44)                            |      |

| 5-15  | Clock Skew Optimization                                       |      |

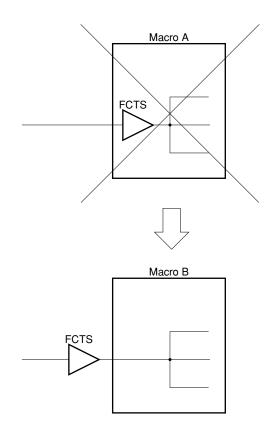

| 5-16  | Example of CTS Block Description                              | 177  |

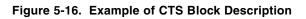

| 5-17  | Configuring High-Speed Operational (Stable) Circuits          |      |

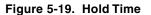

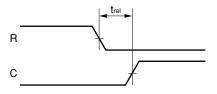

| 5-18  | Setup Time                                                    | 180  |

| 5-19  | Hold Time                                                     |      |

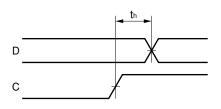

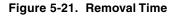

| 5-20  | Release Time                                                  |      |

| 5-21  | Removal Time                                                  |      |

| 5-22  | Minimum Pulse Width                                           |      |

| 5-23  | Example of Delay Time Margin Calculation Circuit              |      |

| 5-24  | Timing Estimate                                               |      |

| 5-25  | Example of In-Phase Clock Circuit                             |      |

| 5-26  | In-Phase Clock Timing                                         |      |

| 5-27  | Example of Inverse-Phase Clock Circuit                        |      |

| 5-28  | Inverse-Phase Clock Timing                                    |      |

| 5-29  | Minimum Pulse Width Estimate                                  |      |

| 5-30  | Pulse Narrowing                                               |      |

| 5-31  | System with Critical Paths                                    |      |

| 5-32  | Example of Input-Input Critical Path                          |      |

| 5-33  | Verification of Setup Time                                    |      |

| 5-34  | Bus Configuration                                             |      |

| 5-35  | Examples of Internal Bus Floating Prevention Circuit          |      |

| 5-36  | External Bus Floating Prevention Countermeasure               |      |

| 5-37  | Flip-Flop Initial Setting                                     |      |

| 5-38  | Counter Division                                              | 197  |

| 5-39  | Racing                                                        | 200  |

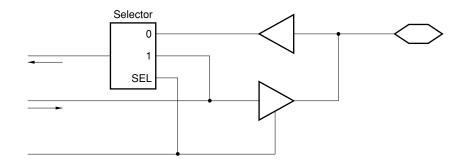

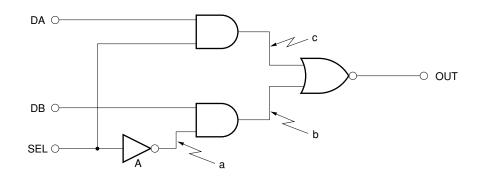

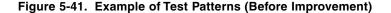

| 5-40  | Example of Data Selector Circuit                              | 201  |

| 5-41  | Example of Test Patterns (Before Improvement)                 | 202  |

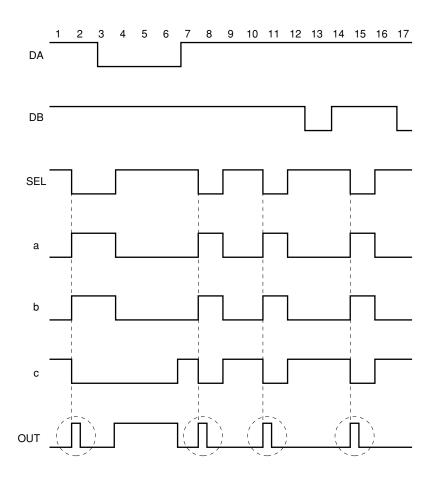

| 5-42  | Example of Test Patterns (After Improvement)                  | 203  |

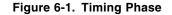

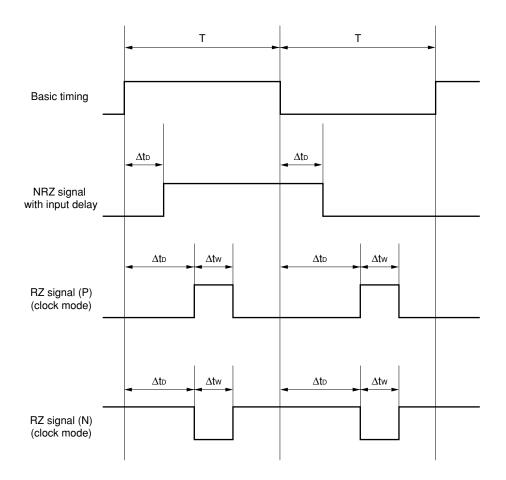

| 6-1   | Timing Phase                                                  |      |

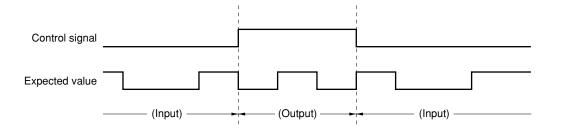

| 6-2   | Example of Incorrect Bidirectional Pin Switch Timing          | 209  |

| 6-3   | Contention During Input/Output Switching                      | 210  |

| 6-4   | Test Pattern Example                                          | 215  |

| 6-5   | Strobe Time                                                   | 216  |

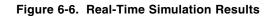

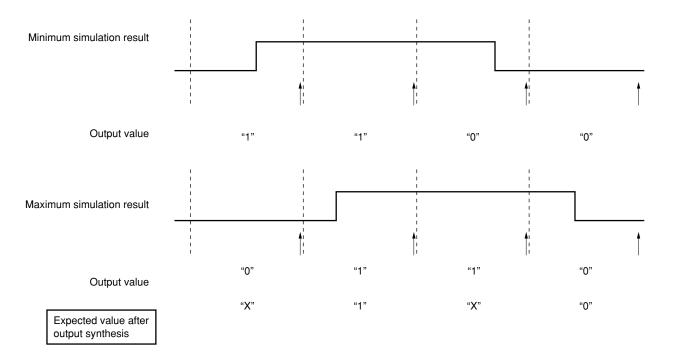

| 6-6   | Real-Time Simulation Results                                  | 218  |

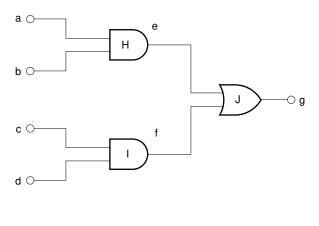

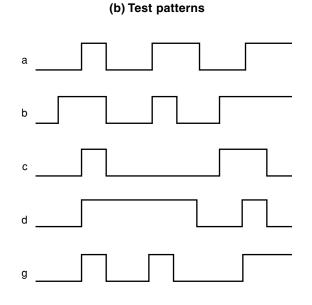

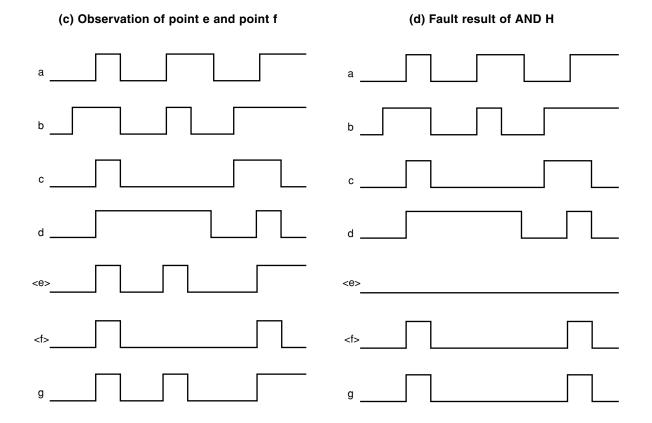

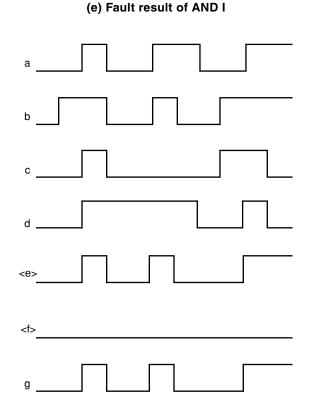

| 6-7   | Concept of Fault Simulation                                   | 220  |

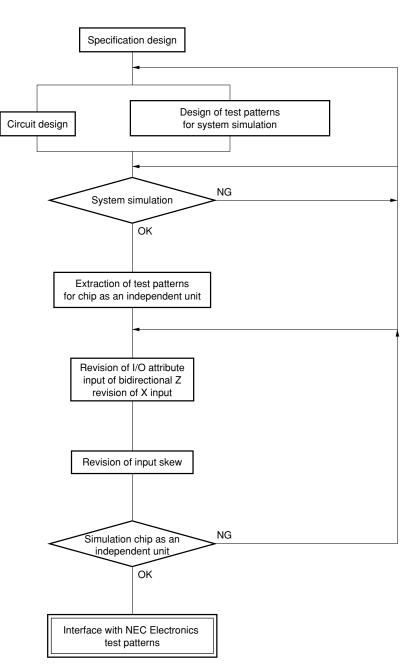

| 6-8   | Creating Test Patterns by System Simulation                   |      |

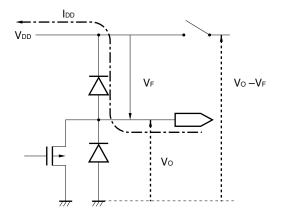

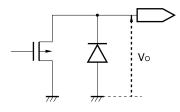

| 7-1   | Equivalent Circuit Diagram for Buffer with Fail-Safe Function |      |

# LIST OF FIGURES (3/3)

| Figure | e No. Title                                  | Page |

|--------|----------------------------------------------|------|

| 7-2    | Example of Oscillator Configuration          |      |

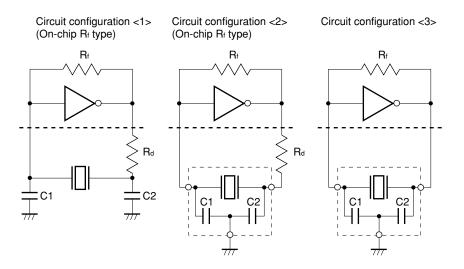

| 7-3    | Oscillator Configuration                     |      |

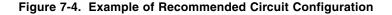

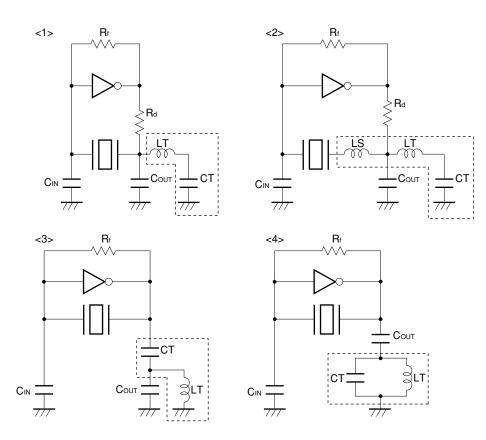

| 7-4    | Example of Recommended Circuit Configuration |      |

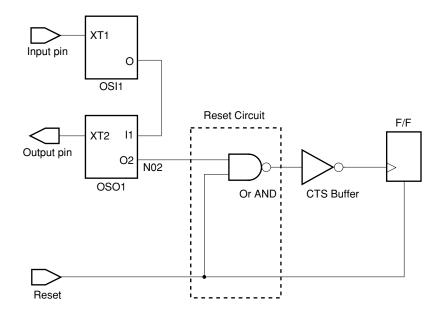

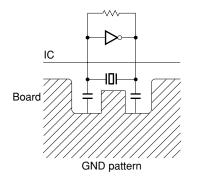

| 7-5    | Example of GND Pattern on Board              |      |

| 7-6    | Example of Overtone Circuits                 |      |

| 7-7    | Oscillator Configuration Diagram             |      |

| 7-8    | Single-Port RAM Circuit Configuration        |      |

| 7-9    | Dual-Port RAM Circuit Configuration          |      |

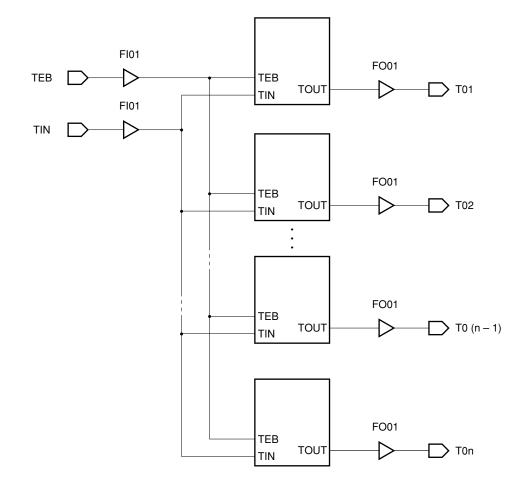

| 7-10   | Test Circuit (BIST) Block Diagram            |      |

| 7-11   | RAM Test Circuits                            |      |

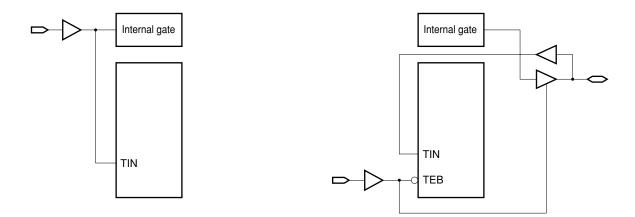

| 7-12   | Making TIN Pin Alternate Function            |      |

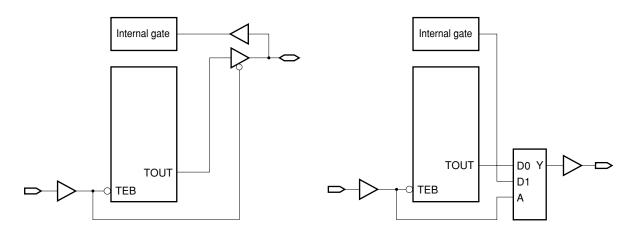

| 7-13   | Making TOUT Pin Alternate Function           |      |

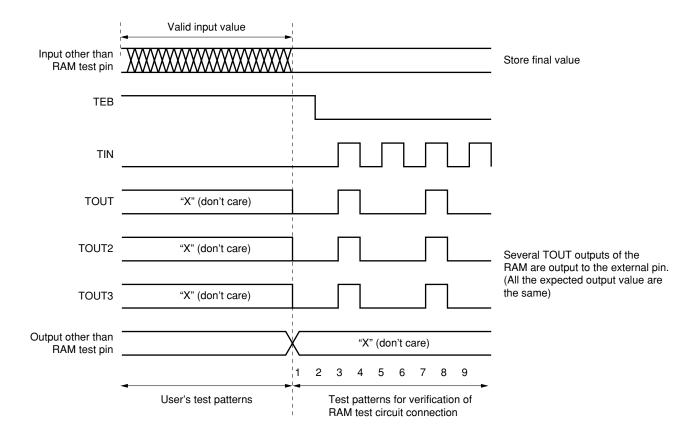

| 7-14   | Example of Test Patterns                     |      |

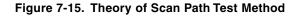

| 7-15   | Theory of Scan Path Test Method              |      |

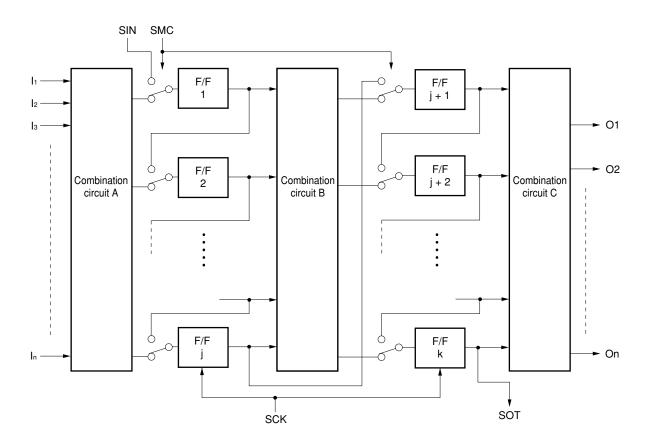

| A-1    | Load Dependency of Power Consumption         |      |

| B-1    | Delay Time Increase Due to Input Waveform    |      |

| D-1    | Circuit Diagram Example                      |      |

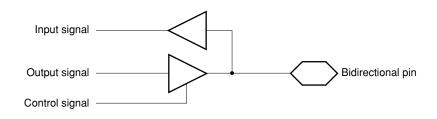

| D-2    | Bidirectional Pin Names                      |      |

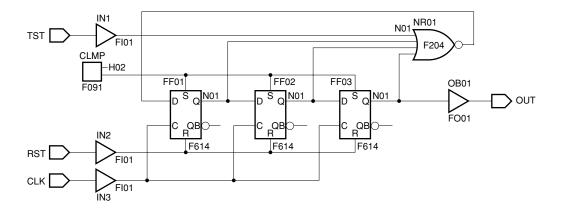

| D-3    | Bidirectional Pin Test Pattern Generation    |      |

| D-4    | 3-State Output Pin Names                     |      |

| D-5    | 3-State Output Pin Test Pattern Generation   |      |

| D-6    | Handling Macros                              |      |

| D-7    | Timing Chart Entry                           |      |

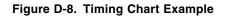

| D-8    | Timing Chart Example                         |      |

# LIST OF TABLES (1/2)

| Table | No. Title                                                                                                                                              | Page |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| 1-1   | Products                                                                                                                                               | 21   |  |

| 2-1   | Number of Cells Placed                                                                                                                                 | 27   |  |

| 2-2   | Usable Gates and Pin-Pair Count                                                                                                                        | 27   |  |

| 2-3   | List of Mountability                                                                                                                                   | 30   |  |

| 2-4   | Minimum Number of Cells Occupied by Basic Macro                                                                                                        | 37   |  |

| 2-5   | Occupied Cell Ranges                                                                                                                                   | 38   |  |

| 3-1   | Terminology for Absolute Maximum Ratings                                                                                                               |      |  |

| 3-2   | Terminology for Recommended Operating Conditions                                                                                                       | 98   |  |

| 3-3   | Terminology for DC Characteristics                                                                                                                     | 99   |  |

| 3-4   | Absolute Maximum Ratings                                                                                                                               | 100  |  |

| 3-5   | Recommended Operating Range (V_DD = 5.0 V $\pm$ 10%, TA = -40 to +85°C)                                                                                | 101  |  |

| 3-6   | DC Characteristics (V <sub>DD</sub> = 5.0 V $\pm$ 10%, T <sub>A</sub> = -40 to +85°C)                                                                  |      |  |

| 3-7   | AC Characteristics (V <sub>DD</sub> = 5.0 V $\pm$ 10%, T <sub>A</sub> = -40 to +85°C)                                                                  |      |  |

| 3-8   | Recommended Operating Range (V_DD = 3.0 $\pm$ 0.3 V, TA = -40 to +85°C)                                                                                |      |  |

| 3-9   | DC Characteristics (V <sub>DD</sub> = $3.0 \pm 0.3$ V, T <sub>A</sub> = $-40$ to $+85^{\circ}$ C)                                                      |      |  |

| 3-10  | AC Characteristics (V <sub>DD</sub> = 3.0 $\pm$ 0.3 V, T <sub>A</sub> = -40 to +85°C)                                                                  |      |  |

| 3-11  | Recommended Operating Range (V_DD = 3.3 $\pm$ 0.3 V, TA = -40 to +85°C)                                                                                |      |  |

| 3-12  | DC Characteristics (V <sub>DD</sub> = $3.3 \pm 0.3$ V, T <sub>A</sub> = $-40$ to $+85^{\circ}$ C)                                                      |      |  |

| 3-13  | AC Characteristics (V <sub>DD</sub> = $3.3 \pm 0.3$ V, T <sub>A</sub> = $-40$ to $+85^{\circ}$ C)                                                      |      |  |

| 3-14  | Capacitance of Interface Block (CB)                                                                                                                    |      |  |

| 3-15  | Capacitance of Packages (CP) (Preliminary Values)                                                                                                      | 110  |  |

| 4-1   | Power Consumption by Input Buffer                                                                                                                      |      |  |

| 4-2   | Output Buffer Power Consumption                                                                                                                        | 120  |  |

| 4-3   | Oscillator Power Consumption (Reference Values) (V <sub>DD</sub> = $5.0 \text{ V} \pm 10\%$ , T <sub>A</sub> = $-40 \text{ to } +85^{\circ}\text{C}$ ) | 121  |  |

| 4-4   | Compensation Coefficient (K1, K2, K3)                                                                                                                  | 126  |  |

| 4-5   | Wiring Capacitance Estimate (Wiring Length Converted to F/I Value)                                                                                     |      |  |

| 4-6   | tr and tr Calculation Coefficients of Output Buffer ( $V_{DD} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}$ )                                             |      |  |

| 4-7   | tr and tr Calculation Coefficients of Output Buffer (VDD = $3.3 \text{ V}$ , TA = $25^{\circ}$ C)                                                      |      |  |

| 4-8   | Recommended Load Capacitance Ranges of Output Buffers (@5.0 V)                                                                                         |      |  |

| 4-9   | Recommended Load Capacitance Ranges of Output Buffers (@3.3 V)                                                                                         |      |  |

| 4-10  | Reference Time Ranges for Simultaneous Operation (TYP.)                                                                                                |      |  |

| 4-11  | Permissible Number of Simultaneous Operation Pins Between 3 GND Pins (IoL = 12 mA)                                                                     |      |  |

| 4-12  | Coefficient of Number of Simultaneous Operation Pins                                                                                                   | 156  |  |

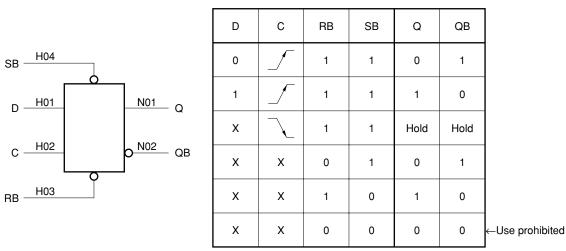

| 5-1   | F617 (D-F/F with RB, SB)                                                                                                                               |      |  |

| 5-2   | Features of Single-Phase and Multi-Phase Synchronous Circuit Design                                                                                    | 166  |  |

| 5-3   | CTS Blocks (Reference)                                                                                                                                 | 174  |  |

| 6-1   | Test Pattern Types                                                                                                                                     | 204  |  |

| 6-2   | Restrictions on Pin Names                                                                                                                              | 205  |  |

# LIST OF TABLES (2/2)

| Table | e No. Title                                               | Page |

|-------|-----------------------------------------------------------|------|

| 6-3   | Limitations on Number of Test Patterns                    | 205  |

| 6-4   | Timing Phase Number                                       | 207  |

| 6-5   | Timing Constraints                                        | 207  |

| 6-6   | Clock Mode                                                | 208  |

| 7-1   | Recommended Oscillation Frequency Range and Configuration |      |

| 7-2   | Example of Criteria                                       | 232  |

| 7-3   | List of Resonator Evaluations                             | 233  |

| 7-4   | Memory Blocks                                             | 235  |

## CHAPTER 1 OVERVIEW

## 1.1 Features

The following table lists the CMOS-N5 Series features.

| Very large-scale integration (VLSI) | 3 K to 120 K gates                                                                                                                                                                                                                                                                                             |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Process                             | 0.5 $\mu$ m rule Si gates, 2-layer metal routing                                                                                                                                                                                                                                                               |

| Input interface                     | CMOS TTL compatible                                                                                                                                                                                                                                                                                            |

| Internal blocks                     | More than 190 types of function blocks<br>Two types are available: high-speed and low-power<br>Scan path block<br>Driver for clock tree synthesis                                                                                                                                                              |

| Memory blocks                       | Single-port RAM<br>Dual-port RAM                                                                                                                                                                                                                                                                               |

| Variety of peripheral blocks        | CMOS TTL level input buffer<br>Input buffer with fail-safe function<br>CMOS level output buffer<br>High drive capability buffer (IoL = 24.0 mA)<br>Low-noise output buffer<br>Buffer with internal pull-up resistor (5 k $\Omega$ /50 k $\Omega$ )<br>Buffer with internal pull-down resistor (50 k $\Omega$ ) |

| Other                               | High latch-up immunity                                                                                                                                                                                                                                                                                         |

The features for each power supply voltage are as follows.

| (1) | Vdd = 5.0 V ±10%         |                                                                                                                                                                                                                                                                                                                  |

|-----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (-) |                          | . tPD = 0.14 ns (2-input NAND (low power gate), fan-outs: 1, wiring length: 0 mm)<br>tPD = 0.21 ns (2-input NAND (low power gate), fan-outs: 1, standard wiring<br>length)<br>tPD = 0.46 ns (2-input NAND (low power gate), fan-outs: 2, wiring length: 2 mm)                                                    |

|     |                          | <ul> <li>tPD = 0.16 ns (2-input NAND, fan-outs: 1, standard wiring length)</li> <li>tPD = 0.30 ns (2-input NAND, fan-outs: 2, wiring length: 2 mm)</li> <li>tPD = 0.18 ns (2-input NAND, fan-outs: 2, standard wiring length)</li> <li>tPD = 0.33 ns (input buffer, fan-outs: 2, wiring length: 2 mm)</li> </ul> |

|     |                          | $t_{PD} = 0.23$ ns (input buffer, fan-outs: 1, standard wiring length)<br>$t_{PD} = 1.30$ ns (output buffer, $C_L = 15$ pF, $I_{OL} = 9$ mA)                                                                                                                                                                     |

|     | Power consumption        | . 1.35 $\mu$ W/MHz/cell (internal gate, operating factor: 0.3)                                                                                                                                                                                                                                                   |

|     | Maximum clock frequency  | .fmax = 200 MHz (internal toggle F/F, fan-outs: 2, wiring length: 0 mm)                                                                                                                                                                                                                                          |

| (2) | Vdd = 3.0 ±0.3 V         |                                                                                                                                                                                                                                                                                                                  |

|     | High-speed operation     | . tPD = 0.20 ns (2-input NAND (low power gate), fan-outs: 1, wiring length: 0 mm)<br>tPD = 0.30 ns (2-input NAND (low power gate), fan-outs: 1, standard wiring length)                                                                                                                                          |

|     |                          | tPD = 0.23 ns (2-input NAND, fan-outs: 1, standard wiring length)                                                                                                                                                                                                                                                |

|     |                          | tpd = 0.42 ns (2-input NAND, fan-outs: 2, wiring length: 2 mm)                                                                                                                                                                                                                                                   |

|     |                          | tPD = 0.26 ns (2-input NAND, fan-outs: 2, standard wiring length)                                                                                                                                                                                                                                                |

|     |                          | $t_{PD} = 0.47$ ns (input buffer, fan-outs: 2, wiring length: 2 mm)                                                                                                                                                                                                                                              |

|     |                          | $t_{PD} = 0.34 \text{ ns}$ (input buffer, fan-outs: 1, standard wiring length)<br>$t_{PD} = 2.16 \text{ ns}$ (output buffer, $C_L = 15 \text{ pF}$ , $I_{OL} = 9 \text{ mA}$ )                                                                                                                                   |

|     | Power consumption        | . 0.49 $\mu$ W/MHz/cell (internal gate, operating factor: 0.3)                                                                                                                                                                                                                                                   |

|     | Maximum clock frequency  | . fMAX = 120 MHz (internal toggle F/F, fan-outs: 2, wiring length: 0 mm)                                                                                                                                                                                                                                         |

| (3) | $V_{DD} = 3.3 \pm 0.3 V$ |                                                                                                                                                                                                                                                                                                                  |

|     | High-speed operation     | . tPD = 0.18 ns (2-input NAND (low power gate), fan-outs: 1, wiring length: 0 mm)<br>tPD = 0.28 ns (2-input NAND (low power gate), fan-outs: 1, standard wiring length)                                                                                                                                          |

|     |                          | tPD = 0.22 ns (2-input NAND, fan-outs: 1, standard wiring length)                                                                                                                                                                                                                                                |

|     |                          | tpp = 0.39 ns (2-input NAND, fan-outs: 2, wiring length: 2 mm)                                                                                                                                                                                                                                                   |

|     |                          | tpp = 0.24 ns (2-input NAND, fan-outs: 2, standard wiring length)                                                                                                                                                                                                                                                |

|     |                          | tPD = 0.44 ns (input buffer, fan-outs: 2, wiring length: 2 mm)                                                                                                                                                                                                                                                   |

|     |                          | tPD = 0.31 ns (input buffer, fan-outs: 1, standard wiring length)                                                                                                                                                                                                                                                |

|     |                          | tPD = 2.02 ns (output buffer, $CL = 15 \text{ pF}$ , $IoL = 9 \text{ mA}$ )                                                                                                                                                                                                                                      |

|     | Power consumption        | 0.59 $\mu$ W/MHz/cell (internal gate, operating factor: 0.3)                                                                                                                                                                                                                                                     |

|     | Maximum clock frequency  | . fMAX = 130 MHz (internal toggle F/F, fan-outs: 2, wiring length: 0 mm)                                                                                                                                                                                                                                         |

#### 1.2 CMOS-N5 Series Products

★

| Master   | Number of Row Gates | Number of Usable Gates |

|----------|---------------------|------------------------|

| μPD65891 | 1920                | 1536                   |

| μPD65880 | 3456                | 2937                   |

| μPD65881 | 5880                | 4998                   |

| µPD65892 | 6692                | 5593                   |

| μPD65882 | 13952               | 11859                  |

| μPD65894 | 15232               | 12185                  |

| µPD65883 | 25344               | 21542                  |

| μPD65884 | 33864               | 28784                  |

| μPD65885 | 40768               | 30576                  |

| μPD65887 | 56496               | 41730                  |

| μPD65889 | 76000               | 57000                  |

| μPD65890 | 99528               | 74646                  |

| μPD65893 | 123384              | 92538                  |

#### Table 1-1. Products

**Remark** Total number of gates integrated on the chip in terms of 2-input NAND (1 cell = 1 gate)

Usable cell rate: μPD65880, 65881, 65882, 65883, 65884 ... 85% μPD65891, 65892, 65894 ... 80% μPD65885, 65887, 65889, 65890, 65893 ... 75%

Design Manual A13826EJ7V0DM

#### 1.3 Internal Structure of CMOS-N5 Series

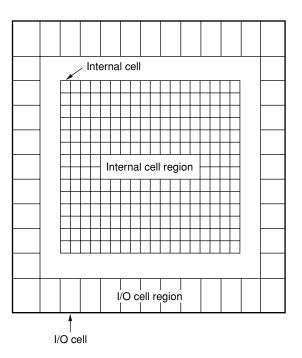

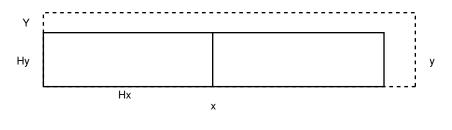

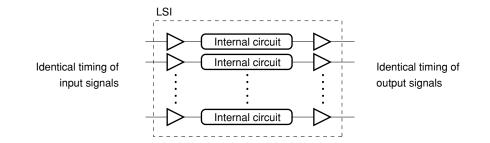

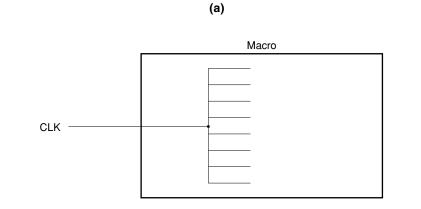

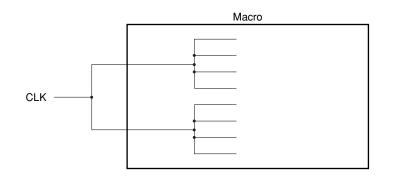

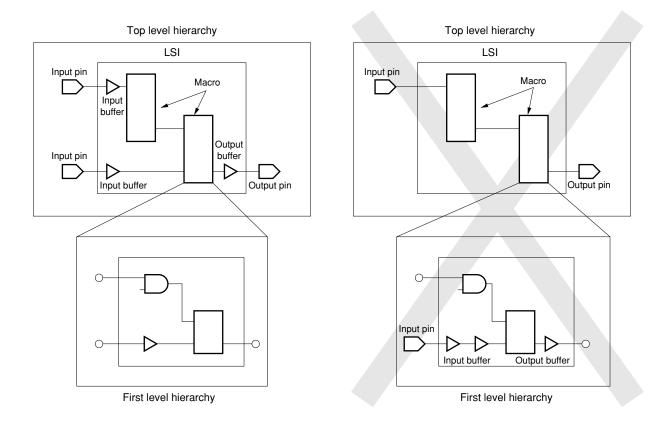

Figure 1-1 shows the CMOS gate array internal structure, which is comprised of an internal cell region and an I/O cell region.

#### Figure 1-1. Gate Array Configuration

As shown in this figure, the CMOS-N5 Series does not have fixed routing regions in the internal cell region, and the entire surface of the internal cell region is filled with basic cells.

The internal cell region consists of various function blocks (such as NAND gates and D-F/F) and memory that are connected via routing layers to implement the desired circuit functions.

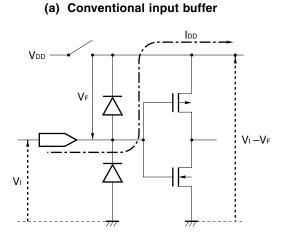

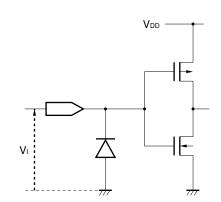

Input and output buffers are placed in the I/O cell region to adjust the input-level conversion and output drive capability. Some internal cells are also part of the I/O buffer implementation.

#### 1.4 Internal Cell Structure

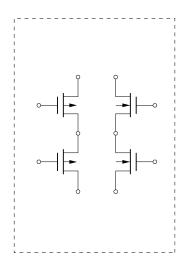

The circuit diagram in Figure 1-2 represents a CMOS-N5 Series internal cell.

Each cell of the CMOS-N5 Series can be configured as a device such as a two-input NAND/NOR gate, an inverter, or a buffer.

A CMOS circuit consists of a P-channel MOS transistor (P-ch. Tr) and an N-channel MOS transistor (N-ch. Tr). Normally, either the P-ch. Tr or the N-ch. Tr is in the OFF state.

#### Figure 1-2. Internal Cell Equivalent Circuit

Because virtually no power flows in the steady state, the power consumption for a CMOS circuit is extremely low.

A CMOS circuit consumes current mostly during switching. Because a high transient current flows during switching, either a high-speed capacitor with a high capacitance must be inserted between the power supply and ground, or the impedance of the power supply lowered.

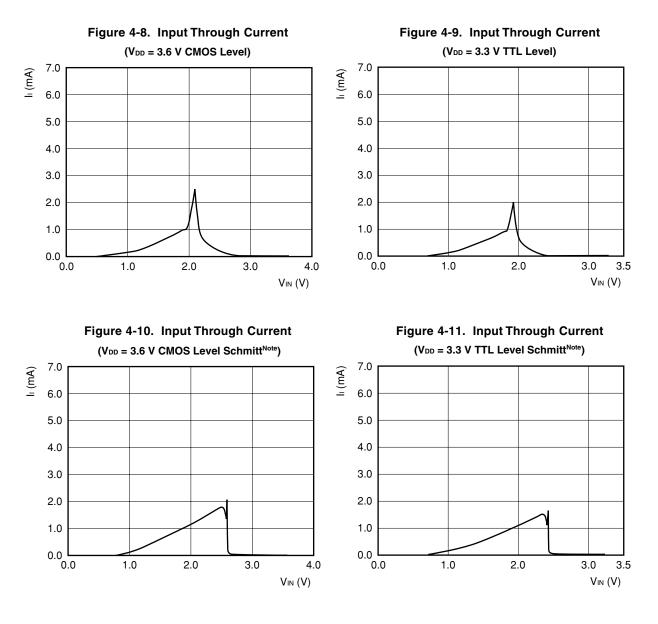

In addition, if a waveform with a slow rise/fall time is applied to a CMOS circuit, both the P-ch. Tr and N-ch. Tr will remain in the ON state for a period of time, causing a through current to flow between the P-ch. Tr and N-ch. Tr, resulting not only in increased current consumption but also possible malfunction.

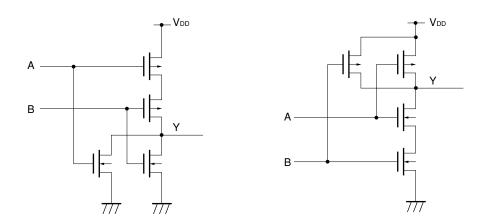

Figure 1-3 (a) and (b) show the equivalent circuits of a 2-input NOR gate and a 2-input NAND gate. Because the ON resistance of the N-ch. Tr is about fifty percent less than that of the P-ch. Tr, a large current can be sent through the N-ch. Tr. Therefore, as shown in Figure 1-3 (a), the ON resistance of the output rise side at the NOR gate, which is serially connected to the P-ch. Tr, becomes larger, and the drive capability of the load drops.

In CMOS gate arrays, the NOR fan-out drive is slower than the NAND fan-out drive. Because of this, the NAND blocks should be used as much as possible to increase the speed and stability of the circuit.

For the same reason, complex gates that serially connect many transistors tend to be slow, and therefore should not be used in high-speed circuits. Use complex gates to improve cell utilization when speed is not as important.

#### Figure 1-3. Equivalent Circuits

#### (a) 2-Input NOR Equivalent Circuit

#### (b) 2-Input NAND Equivalent Circuit

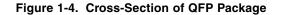

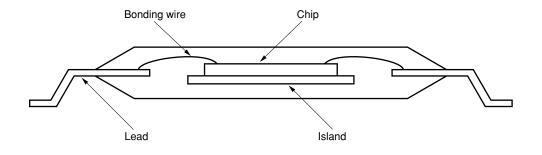

#### 1.5 QFP Package

Figure 1-4 shows a cross-section of a normal QFP package. In a normal QFP package, the chip is placed on a metal plate called an island. The leads and chip are connected by fine bonding wires measuring only several 10  $\mu$ m in diameter.

In a low thermal resistance type QFP package, the lead and island materials have increased thermal dissipation properties. The construction itself is the same as a normal QFP package.

#### CHAPTER 2 IMPLEMENTING THE SYSTEM USING THE GATE ARRAY

Be sure to read this chapter since it describes the information that is important when starting design. When using gate arrays to develop an LSI to implement some or all of a system designed by the user, the specifications must be determined so that the circuit scale and the number of I/O pins of the gate arrays are optimum.

As the circuit scale increases, designing the circuit becomes more difficult and the cost of the LSI increases. However, because the number of I/O pins can be reduced, so can the mounting area on a printed wiring board.

In addition, because the number of LSIs used decreases, the propagation delay time is shortened.

However, as the circuit scale decreases, many separate gate arrays are required to configure the system. This is disadvantageous in terms of printed circuit board mounting. Moreover, because signals are transferred between many LSIs, it is difficult to shorten the propagation delay time.

Therefore, when selecting a gate array, take into consideration the propagation delay time and circuit scale. Select a gate array in the following steps.

#### [Circuit selection steps]

- (1) Estimate circuit scale and master size

- $\downarrow$

- (2) Select package

- (3) Verify power consumption

- $\downarrow$

- (4) Verify pin placement  $\downarrow$

- (5) Verify I/O interface level  $\downarrow$

- (6) Design circuit

- $\downarrow$

- (7) Interface  $\downarrow$

- (8) Check using the check items

#### 2.1 Estimating Circuit Scale

#### 2.1.1 Cell utilization rate, usable cell and pin-pair count limits

In a channel architecture gate array, the internal cell region is divided into two regions.

- · Region where transistors that implement the function block are placed

- · Routing dedicated region

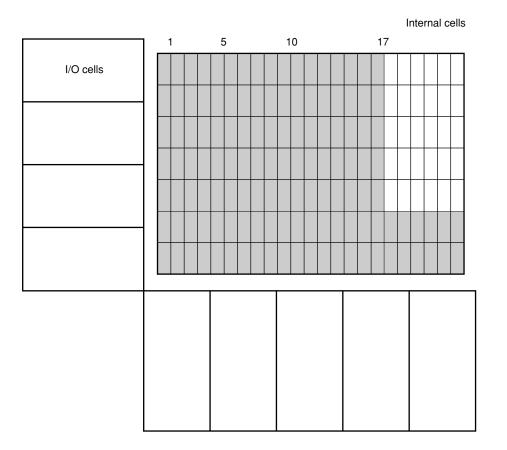

In a channelless architecture gate array, the region for implementing the function blocks cannot be clearly distinguished from the routing region because the transistors that implement the function blocks are laid out over the entire internal cell region. Consequently, there is a stronger correlation between the number of cells utilized and the number of nets.

The CMOS-N5 Series uses a channelless architecture (sea-of-gates). This means that not all cells in the internal cell region can be used for function blocks such as gates, flip-flops, and memory. The number of cells actually used is the difference between the total number of cells and the routing cell region used by the number of wires between blocks (number of pin pairs).

The maximum cell utilization rate for the CMOS-N5 Series is as follows.

| * |  |

|---|--|

| * |  |

| μPD65880, 65881, 65882, 65883, 65884 : 85% |  |

|--------------------------------------------|--|

| μPD65891, 65892, 65894 : 80%               |  |

| μPD65885, 65887, 65889, 65890, 65893 : 75% |  |

However, if a large-scale block, such as memory, is placed, it may be that the total cell utilization rate is further limited, depending on the type of macro (see **2.1.3 Large-scale macro mounting** for details).

The pin-pair count is limited by the cell utilization rate and can be calculated by the following formula:

```